14th March 2023

I've updated my logic analysis system. The old one was a HP 16602A - 102 channels (not upgradeable) with 100MHz state and 500MHz timing analysis. It was running HP-UX and took a long while to boot, but once running it actually worked well. I spotted an Agilent 16902A for sale locally in Australia though (it's quite rare to see these pop up for sale here), and after some negotiation I was able to purchase it.

It's in mint condition and included 2 x 68 channel 16950A cards. These cards can do 600MHz state and 4Ghz timing analysis so quite a bit faster than the old. Thanks to an EEVBLOG forum member I was able to get the full 64M aquisition memory unlocked on each card (they were 256K but HP/Agilent/Keysight has a licensing mechanism to unlock the full 64M that is installed on each card). I also built a VM on my main PC and installed the logic analysis software on it so that I could run a much more useful 2560 x 1080 resolution versus the inbuilt LCD touch panel (wider = better). So I boot the logic analysis system to the login screen, and then launch the logic analysis application on my VM. It then connects to the mainframe over ethernet, and has full control of the capture cards.

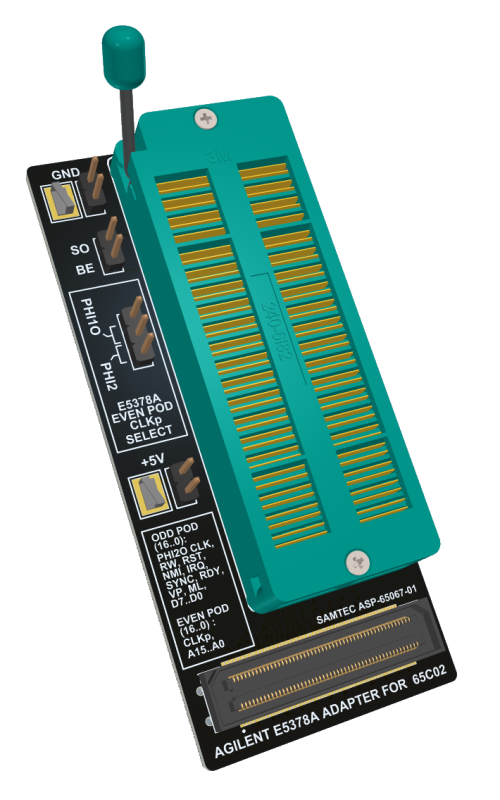

Next, I designed a PCB that allows me to connect the logic analysis system to a 6502/65C02 cpu using only a single connector. This required me to purchase the Agilent E5378A adapter cable which adapts 2 x 90 pin pod cables from one of the 16950A cards to a 100 pin Samtec connector. The mating Samtec is installed on my 65C02 adapter board. A nice fast setup (I had designed a similar board for the old HP 16602A).

Following that, I recompiled Phil Pembertons 65C02 inverse assembler (fixing a small branch prediction bug on the way) and built a .dll file that can be installed on the 169xx series logic analysis systems - again with thanks to the same EEVBLOG forum member for guiding me through the process of setting up the build environment. The inverse assembler allows code analysis - you can see each and every instruction that is being fetched and executed by the CPU and can set up triggers around this. So that will now give me the functionality I had with the old unit, but with a whole lot more headroom and better useability. Plus the 16902A actually has 6 slots and I'm only using 2 - I could add a lot more channels if I ever need them, but 136 will do for now :)

This new logic analysis system will be handy for the current project we are working on - Gyve.

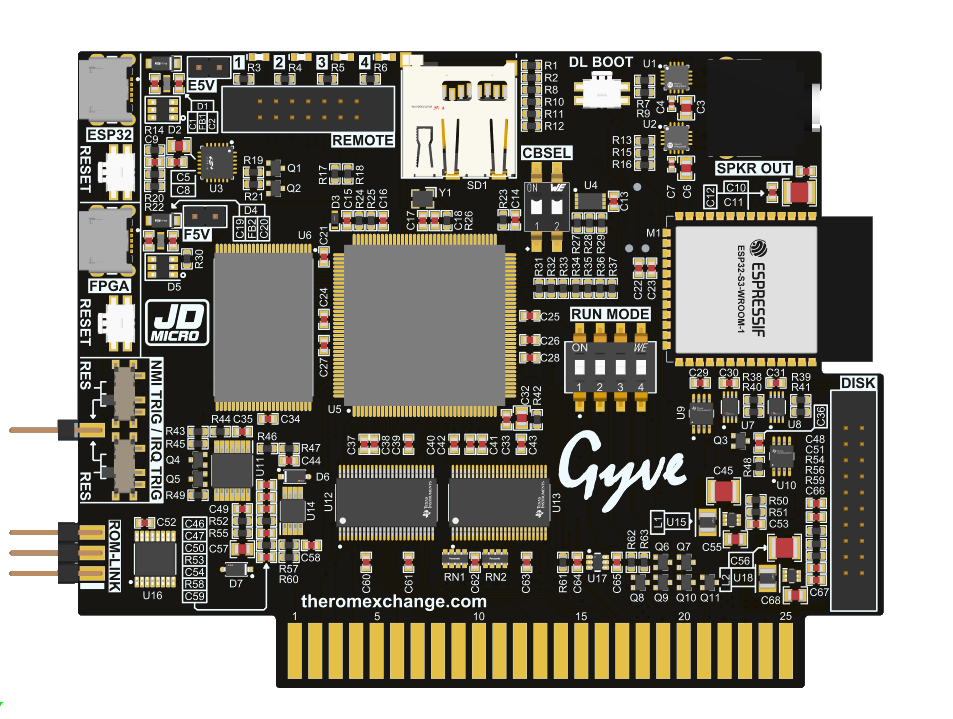

A while back I posted some photos of a handwired prototype. Nothing more has been done with that as the CPLD I was going to use is very difficult to get hold of at present. So the design was reworked with an iCE40 FPGA, and a board was laid out :

Gyve features an ESP32-S3 for the WiFi capability, which will be configued to run FujiNet software. Both the FPGA and ESP are user programmable via USB, and it also has a 16Mbit flash chip so as it could be configured to run as a ROMX including the ROM-Link functionality for video ROM's. Connected to the ESP are a pair of audio amps with a 3.5mm jack for speakers, and the uSD card. There is a header for a "remote control" board, which includes an I2C interface for LCD or what-have-you, some LED's, a rotary encoder with switch (volume or menu control), and also a switch for the interrupt generator capability that is inbuilt (NMI or IRQ can be generated either by external switch or by the Apple //e reset button when pressed alone). There is also a disk header there for connection of a physical disk drive via an adapter cable (the header is 2.00mm pitch and includes both drive enables as well as the 3.5" enable so an adapter would plug into this to break it out to 2 x 20 pin headers or a DB19). So there is a fair bit going on and I'm bound to have cocked something up, but this is Rev 1 and we'll see how far we get with it :)

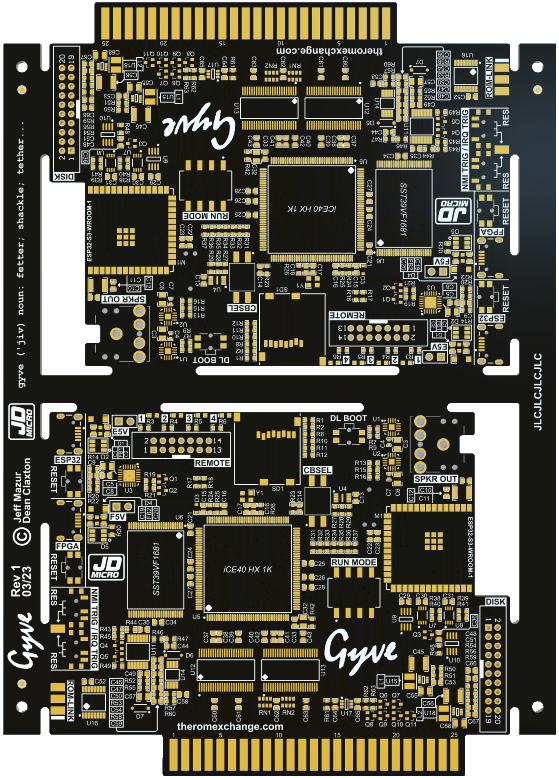

I also did a small panel with 2 boards on it, which will allow me to assemble a couple at a time :

So now I need to get these boards made and then were are into the coding side of things to bring it up for the first time - Fun stuff :)